System Verilog for Verification

- Last Updated 01/2025

- English

- English[Integrated]

A comprehensive online course that covers all the constructs in System verilog. Description of each construct along with examples and coding assignments enable thorough learning

What will you learn?

-

Basic building blocks - Module, Program block, function, task and class

- Data types and its uses

- Parallel processing thread - initial begin, always, fork join and fine grain process control

- Object Oriented Programming (OOP)

- Connecting the testbench and design

- Inter process synchronisation and communication

- Randomization and constraints

- Functional coverage

Price Rs.14,900 (inclusive of GST)

Instructor Viswa Krishnamurthi

Duration 13 Weeks

Chapters 11

Learners 380 students

This Course Includes

- 8 hours on-demand video

- Lab assignments

- Quizzes and Elaborate Questions

- Certificate of completion

Certificate for completion (80%):

The certificate will state:

“This is to certify that (Name) has actively participated

in the course ‘Digital Design and Verification’ and completed a major portion of the curriculum”

Certificate for completion (95% or more):

The certificate will state:

“This is to verify that(Name) has successfully

completed the course ‘Digital Design and Verification'”

Course Curriculum

11 Chapters 54 Lectures 8h total length

Video Preview with Icon Introduction_________________________________________________________________________________________________________________ 1 lecture 2min

Introduction_________________________________________________________________________________________________________________ 1 lecture 2min

- Introduction - --------------------------------------------------------------------------------------------------------02:53

Video Preview with Icon Basic Building Blocks _ _______________________________________________________________________________ </> Lab __________ _ 8 lectures 40min

Basic Building Blocks _ _______________________________________________________________________________ </> Lab __________ _ 8 lectures 40min

- Introduction------------------------------------------------------------------------------------------------------------03.41

- Basic building blocks_intro-----------------------------------------------------------------------------------------------11:40

- Module-------------------------------------------------------------------------- --------------------------------------05:22

- Program Block----------------------------------------------------------------------------------------------------------02:05

- Functions--------------------------------------------------------------------------------------------------------- -----03:35

- Tasks----------------------------------------------------------------------------------------------------------------- -07:27

- Class- -----------------------------------------------------------------------------------------------------------------04:00

- Basic built in system routines---------------------------------------------------------------------------------------------03:12

Video Preview with Icon Data types_ ___________________________________________________________________________________________ </> Lab __________ _ 13 lectures 14min

Data types_ ___________________________________________________________________________________________ </> Lab __________ _ 13 lectures 14min

- Literals values-------- --------------------------------------------------------------------------------------------------06:55

- String------------------------------------------------------------------------------------------------------------------04:59

- Array-------------------------------------------------------------------------------------------------------------------10:20

- Dynamic Array - --------------------------------------------------------------------------------------------------------03:49

- Associative Array - ------------------------------------------------------------------------------------------------------09:46

- Queue------------------------------------------------------------------------------------------------------------------05:06

- Array Manipulation Methods - -------------------------------------------------------------------------------------------- 05:53

- user defined types - -----------------------------------------------------------------------------------------------------04:15

- Enumeration - --------------------------------------------------------------------------------------------------------- -07:51

- Structure - ------------------------------------------------------------------------------------------------------------ -03:53

- Union - --------------------------------------------------------------------------------------------------------------- -03:57

- Events------------------------------------------------------------------------------------------------------------------12:40

- Scope and Lifetime - ---------------------------------------------------------------------------------------------------- 04:23

Video Preview with Icon Operators____________________________________________________________________________________________ _ </> Lab __________ _ 2 lectures 13min

Operators____________________________________________________________________________________________ _ </> Lab __________ _ 2 lectures 13min

- Operators---------------------------------------------------------------------------------------------------------------07:46

- Streaming operators-----------------------------------------------------------------------------------------------------06:05

Video Preview with Icon Procedural and control flow___________________________________________________________________________</> Lab __________ _ 7 lectures 55min

Procedural and control flow___________________________________________________________________________</> Lab __________ _ 7 lectures 55min

- Sub routines--------------------------------------------------------------------------------------------------------------18:18

- Blocking and non-blocking-------------------------------------------------------------------------------------------------06:52

- Regions and Scheduling ---------------------------------------------------------------------------------------------------09:30

- Selection statements----------------------------------------------------------------------------------------------------- -04:17

- Loop statements - ------------------------------------------------------------------------------------------------------- -09:14

- Jump statements - ------------------------------------------------------------------------------------------------------- 04:06

- Disable and named block - ------------------------------------------------------------------------------------------------03:10

Video Preview with Icon Processes_____________________________________________________________________________________________ _</> Lab __________ _ 4 lectures 37min

Processes_____________________________________________________________________________________________ _</> Lab __________ _ 4 lectures 37min

- Initial begin, always -----------------------------------------------------------------------------------------------------06:48

- Fork join----------------------------------------------------------------------------------------------------------------16:15

- Fine-grain process control -----------------------------------------------------------------------------------------------12:04

- Final block--------------------------------------------------------------------------------------------------------------02:20

Video Preview with Icon Connecting the testbench and design _______________________________________________________________ </> Lab __________ _ 4 lectures 38min

Connecting the testbench and design _______________________________________________________________ </> Lab __________ _ 4 lectures 38min

- Connecting testbench and design_intro------------------------------------------------------------------------------------05:23

- Interface----------------------------------------------------------------------------------------------------------------24:54

- Program block-----------------------------------------------------------------------------------------------------------04:00

- Package-----------------------------------------------------------------------------------------------------------------04:10

Video Preview with Icon OOP ___________________________________________________________________________________________________</> Lab ____________ 5 lectures 63min

OOP ___________________________________________________________________________________________________</> Lab ____________ 5 lectures 63min

- Introduction-------------------------------------------------------------------------------------------------------------06:21

- Class I------------------------------------------------------------------------------------------------------------------18:56

- Class II -----------------------------------------------------------------------------------------------------------------13:25

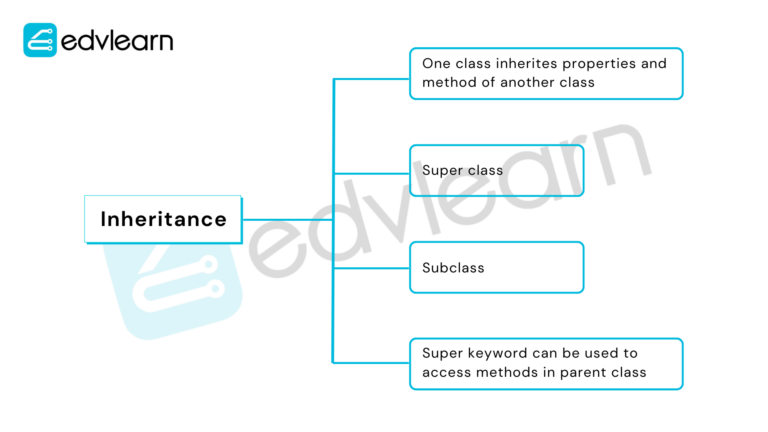

- Inheritance--------------------------------------------------------------------------------------------------------------14:25

- Polymorphism-----------------------------------------------------------------------------------------------------------10:46

Video Preview with Icon Randomization and Constraints ______________________________________________________ _ _____________ </> Lab___________ _ 4 lectures 54min

Randomization and Constraints ______________________________________________________ _ _____________ </> Lab___________ _ 4 lectures 54min

- Intro-------------------------------------------------------------------------------------------------------------------07:50

- Randomization----------------------------------------------------------------------------------------------------------14:39

- Constraints-------------------------------------------------------------------------------------------------------------23:43

- Randomization and Constraints control------------------------------------------------------------------------------------08:01

Video Preview with Icon Inter process synchronization and communication ________________________________________________ _</> Lab ____________ 3 lectures 30min

Inter process synchronization and communication ________________________________________________ _</> Lab ____________ 3 lectures 30min

- Intro-------------------------------------------------------------------------------------------------------------------01:12

- Mailbox----------------------------------------------------------------------------------------------------------------25:05

- Semaphore ------------------------------------------------------------------------------------------------------------04:22

Video Preview with Icon Functional coverage and DPI________________________________________________________________________ _</> Lab ____________ 3 lectures 25min

Functional coverage and DPI________________________________________________________________________ _</> Lab ____________ 3 lectures 25min

- Functional Coverage intro ------------------------------------------------------------------------------------------------10:07

- Bin ---------------------------------------------------------------------------------------------------------------------09:47

- Coverpoint -------- -----------------------------------------------------------------------------------------------------05:41

- Covergroup

- Cross coverage

- Coverage options

- Coverage methods

- DPI

Meet Your Instructor

Viswa Krishnamurthi

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience.

Basic knowledge of digital design and programming

Pre-requisite

How it works?

Register

Sign up to gain access to the course

How it works?

How it works?

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Learn and Apply

Complete the course videos, exercises, and the exam

Get Certified

Share your certificates on LinkedIn and enhance your professional growth

To become a VLSI engineer, you need a good foundation in digital electronics. Proficiency in hardware description languages (HDL) like Verilog or VHDL and programming skills are essential for designing and verifying circuits. Strong problem-solving and analytical thinking skills help in optimizing designs.

Additionally, knowledge of simulation tools and debugging techniques can be beneficial. You should be comfortable to code

Yes! Our courses are designed to be beginner-friendly, with a structured curriculum that starts with the fundamentals before moving to advanced topics. Additionally, our trainers are available to assist you throughout your learning journey. Knowledge in programming helps in understanding the course.

System Verilog for Verification

- Last Updated 01/2025

- English

- English[Integrated]

A comprehensive online course that covers all the constructs in System verilog. Description of each construct along with examples and coding assignments enable thorough learning

What will you learn?

- Basic building blocks - Module, Program block, function, Task and Class

- Data types and its uses

- Parallel processing thread - initial begin, always, fork join and fine grain process control

- Object Oriented programming (OOP)

- Connecting the testbench and design

- Inter process synchronisation and communication

- Randomization and constraints

- Functional coverage

Price Rs.14,900 (inclusive of GST)

Instructor Viswa Krishnamurthi

Duration 13 Weeks

Chapters 10

Learners 380 students

This Course Includes:

- 7 hours on-demand video

- Lab assignments

- Quizzes and Elaborate Questions

- Certificate of completion

Certificate for completion (80%):

The certificate will state:

“This is to certify that (Name) has actively participated in the course ‘Digital Design and Verification’ and completed a major portion of the curriculum”

Certificate for completion (95% or more):

The certificate will state:

“This is to verify that(Name) has successfully completed the course ‘Digital Design and Verification'”

Course Curriculum

14 Chapters 74 Lectures 7h total length

Video Preview with Icon Introduction _______________________________________________________ _ 1 lecture 2min

Introduction _______________________________________________________ _ 1 lecture 2min

- Introduction -------------------------------------------------------------02.53

Video Preview with Icon Basic Building Blocks ____________________________ </> Lab _______ _ 8 lectures 40min

Basic Building Blocks ____________________________ </> Lab _______ _ 8 lectures 40min

- Introduction -------------------------------------------------------------03.41

- Basic Building blocks_intro----------------------------------------------- -11:40

- Module-------------- ----------------------------------------------------05:22

- Program block----------------------------------------------------------- 02:05

- Functions----------------------------------------------------------------03:35

- Tasks------------------------------------------------------------------- 07:27

- Class------------------------------------------------------------------- 04:00

- Basic built-in system routines----------------------------------------------03:12

Video Preview with Icon Data types________________________________________ </> Lab _______ _ 13 lectures 83min

Data types________________________________________ </> Lab _______ _ 13 lectures 83min

- Literals values------------------------------------------------------------06:55

- String------------------------------------------------------------------- 04:59

- Array --------------------------------------------------------------------10:20

- Dynamic Array - ----------------------------------------------------------03:49

- Associative Array - ------------------------------------------------------ -09:46

- Queue - -----------------------------------------------------------------05:06

- Array manipulation methods - ---------------------------------------------05:53

- User defined types - ----------------------------------------------------- -04:15

- Enumeration - ---------------------------------------------------------- -07:51

- Structure - ---------------------------------------------------------------03:53

- Union - ------------------------------------------------------------------03:57

- Events - ------------------------------------------------------------------12:40

- Scope and Lifetime - ------------------------------------------------------04:23

Video Preview with Icon Operators _________________________________________</> Lab _______ _ 2 lectures 13min

Operators _________________________________________</> Lab _______ _ 2 lectures 13min

- Operators ------------------------------------------------------------- 07:46

- Streaming operators----------------------------------------------------06:05

Video Preview with Icon Procedural and control flow_____________________ _</> Lab _________ 7 lectures 55min

Procedural and control flow_____________________ _</> Lab _________ 7 lectures 55min

- Sub routines-------------------------------------------------------------18:18

- Blocking and non-blocking------------------------------------------------06:52

- Regions and Scheduling------------------------------------------------- -09:30

- Selection statements-----------------------------------------------------04:17

- Loop statements ------------------------------------------------------- -09:14

- Jump statements ------------------------------------------------------ -04:06

- Disable and named block ----------------------------------------------- -03:10

Video Preview with Icon Processes ________________________________________ _</> Lab _______ _ 4 lectures 37min

Processes ________________________________________ _</> Lab _______ _ 4 lectures 37min

- Initial begin, always------------------------------------------------------06:48

- Fork join---------------------------------------------------------------- 16:15

- Fine-grain process control------------------------------------------------12:04

- Final block --------------------------------------------------------------02:20

Video Preview with Icon Connecting the testbench and design ___________</> Lab _________ 4 lectures 38min

Connecting the testbench and design ___________</> Lab _________ 4 lectures 38min

- Connecting testbench and design_intro------------------------------------05:23

- Interface---------------------------------------------------------------- 24:54

- Program block -----------------------------------------------------------04:00

- Package-----------------------------------------------------------------04:10

Video Preview with Icon OOP _____________________________________________ _ </> Lab _ _______ 5 lectures 63min

OOP _____________________________________________ _ </> Lab _ _______ 5 lectures 63min

- Introduction-------------------------------------------------------------06:21

- Class I------------------------------------------------------------------18:56

- Class II ---------------------------------------------------------------- -13:25

- Inheritance--------------------------------------------------------------14:25

- Polymorphism-----------------------------------------------------------10:46

Video Preview with Icon Randomization and Constraints ________________ _ </> Lab _______ _ 4 lectures 54min

Randomization and Constraints ________________ _ </> Lab _______ _ 4 lectures 54min

- Intro--------------------------------------------------------------------07:50

- Randomization---------------------------------------------------------- 14:39

- Constraints ------------------------------------------------------------- 23:43

- Randomization and Constraints control------------------------------------ 08:01

Video Preview with Icon Inter process synchronization and communication_____ </> Lab __ 3 lectures 30min

Inter process synchronization and communication_____ </> Lab __ 3 lectures 30min

- Intro-------------------------------------------------------------------- 01:12

- Mailbox------------------------------------------------------------------25:05

- Semaphore--------------------------------------------------------------04:22

Video Preview with Icon Functional coverage and DPI _____________________ </> Lab _________ 3 lectures 25min

Functional coverage and DPI _____________________ </> Lab _________ 3 lectures 25min

- Functional Coverage intro ------------------------------------------------10:07

- Bin---------------------------------------------------------------------09:47

- Coverpoint ------------------------------------------------------------- 05:41

- Covergroup

- Cross coverage

- Coverage options

- Coverage methods

- DPI

Meet Your Instructor

Viswa Krishnamurthi

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience

Basic knowledge of digital design and programming

Pre-requisite

How it works?

How it works?

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Register

Sign up to gain access to the course

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Learn and Apply

Complete the course videos, exercises, and the exam.

Get Certified

Share your certificates on LinkedIn and enhance your professional growth

To become a VLSI engineer, you need a good foundation in digital electronics. Proficiency in hardware description languages (HDL) like Verilog or VHDL and programming skills are essential for designing and verifying circuits. Strong problem-solving and analytical thinking skills help in optimizing designs.

Additionally, knowledge of simulation tools and debugging techniques can be beneficial. You should be comfortable to code

Yes! Our courses are designed to be beginner-friendly, with a structured curriculum that starts with the fundamentals before moving to advanced topics. Additionally, our trainers are available to assist you throughout your learning journey. Knowledge in programming helps in understanding the course.

System Verilog for Verification

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience

- Last Updated 01/2025

- English

- English[Integrated]

What will you learn?

- Basic building blocks - Module, Program block, function, Task and Class

- Data types and its uses

- Parallel processing thread - initial begin, always, fork join and fine grain process control

- Object Oriented programming (OOP)

- Connecting the testbench and design

- Inter process synchronisation and communication

- Randomization and constraints

- Functional coverage

Price Rs.14,900 (incl. of GST)

Instructor Viswa Krishnamurthi

Duration 13 Weeks

Chapters 10

Learners 380 students

This Course Includes

- 5 hours on-demand video

- Lab assignments

- Quizzes and Elaborate Questions

- Certificate of completion

Certificate for completion (80%):

The certificate will state:

“This is to certify that (Name) has actively participated in the course ‘Digital Design and Verification’ and completed a major portion of the curriculum”

Certificate for completion (95% or more):

The certificate will state:

“This is to verify that(Name) has successfully completed the course ‘Digital Design and Verification'”

Course Curriculum

14 Chapters 74 Lectures 5h total length

Video Preview with Icon Introduction___ 1 lecture 2min

Introduction___ 1 lecture 2min

- Introduction ------------02.53

Video Preview with Icon Basic building blocks___ </> Lab _____ 8 lectures 40min

Basic building blocks___ </> Lab _____ 8 lectures 40min

- Introduction------------03.41

- Basic building blocks_intro-----------------------------11:40

- Module----------------05:22

- Program Block------ ---02:05

- Functions--------------03:35

- Tasks----------------- 07:27

- Class---------------- -04:40

- Basic built in system routines---------------------------03:12

Video Preview with Icon Data types______________ </> Lab _____ 13 lectures 14min

Data types______________ </> Lab _____ 13 lectures 14min

- Literals values----------06:55

- String---------------- -04:59

- Array------------------10:20

- Dynamic Array---------03:49

- Associative Array-------09:46

- Queue ----------------05:06

- Array manipulation methods------------------------- -05:53

- User defined types------04:15

- Enumeration -----------07:51

- Structure --------------03:53

- Union -----------------03:57

- Events --------------- -12:40

- Scope and Lifetime-----04:23

Video Preview with Icon Operators_______________ </> Lab _____ 2 lectures 13min

Operators_______________ </> Lab _____ 2 lectures 13min

- Operators-------------07:46

- Streaming operators--------------- ------------------06:05

Video Preview with Icon Procedural and control flow_____________________ </> Lab _____ 7 lectures 55min

Procedural and control flow_____________________ </> Lab _____ 7 lectures 55min

- Sub routines------------18:18

- Blocking and non-blocking-----------------------------06:52

- Regions and Scheduling-09:30

- Selection statements----04:17

- Loop statements--------09:14

- Jump statements-------04:06

- Disable and named block--------------------------- ---03:10

Video Preview with Icon Processes_______________ </> Lab ____ _ 4 lectures 37min

Processes_______________ </> Lab ____ _ 4 lectures 37min

- Initial begin, always----06:48

- Fork join-------------- 16:15

- Fine-grain process control----------------------------12:04

- Final block ------------02:20

Video Preview with Icon Connecting the testbench and design_________________ _ </> Lab ______ 4 lectures 38min

Connecting the testbench and design_________________ _ </> Lab ______ 4 lectures 38min

- Connecting testbench and design_intro----------05:23

- Interface------------- 24:54

- Program block --------04:00

- Package--------------04:10

Video Preview with Icon OOP_____________________ </> Lab ______ 5 lectures 63min

OOP_____________________ </> Lab ______ 5 lectures 63min

- Introduction------------06:21

- Class I-----------------18:56

- Class II-----------------13:25

- Inheritance-------------14:25

- Polymorphism----------10:46

Video Preview with Icon Randomization and Constraints______________ </> Lab ______ 4 lectures 54min

Randomization and Constraints______________ </> Lab ______ 4 lectures 54min

- Intro------------------07:50

- Randomization---------14:39

- Constraints------------23:43

- Randomization and Constraints control----------------08:01

Video Preview with Icon Inter process synchronization and communication_________ </> Lab ______ 3 lectures 30min

Inter process synchronization and communication_________ </> Lab ______ 3 lectures 30min

- Intro--------------------01:12

- Mailbox-----------------25:05

- Semaphore -------------04:22

Video Preview with Icon Functional coverage and DPI_______________________ </> Lab _______ 3 lectures 25min

Functional coverage and DPI_______________________ </> Lab _______ 3 lectures 25min

- Functional Coverage intro------------------------------10:07

- Bin --------------------09:47

- Coverpoint ------------ 05:41

- Covergroup

- Cross coverage

- Coverage options

- Coverage methods

- DPI

Meet Your Instructor

Viswa Krishnamurthi

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience.

Pre-requisite

Basic knowledge of digital design and programming

How it works?

Register

Sign up to gain access to the course

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Learn and Apply

Complete the course videos, exercises, and the exam.

Get Certified

Share your certificates on LinkedIn and enhance your professional growth

To become a VLSI engineer, you need a good foundation in digital electronics. Proficiency in hardware description languages (HDL) like Verilog or VHDL and programming skills are essential for designing and verifying circuits. Strong problem-solving and analytical thinking skills help in optimizing designs.

Additionally, knowledge of simulation tools and debugging techniques can be beneficial. You should be comfortable to code

Yes! Our courses are designed to be beginner-friendly, with a structured curriculum that starts with the fundamentals before moving to advanced topics. Additionally, our trainers are available to assist you throughout your learning journey. Knowledge in programming helps in understanding the course.