Writing System Verilog

Testbench

- Last Updated 01/2025

- English

- English[Integrated]

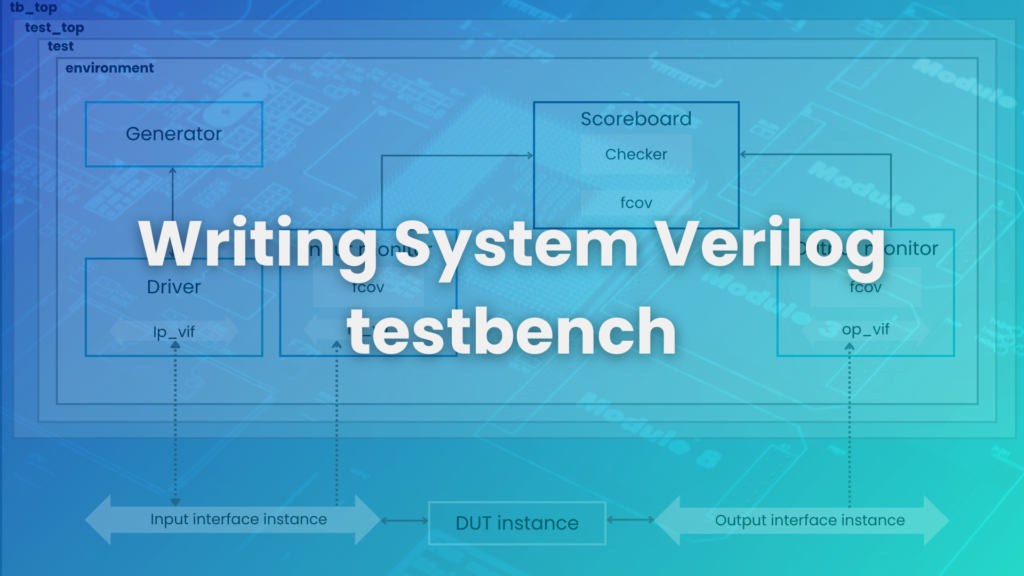

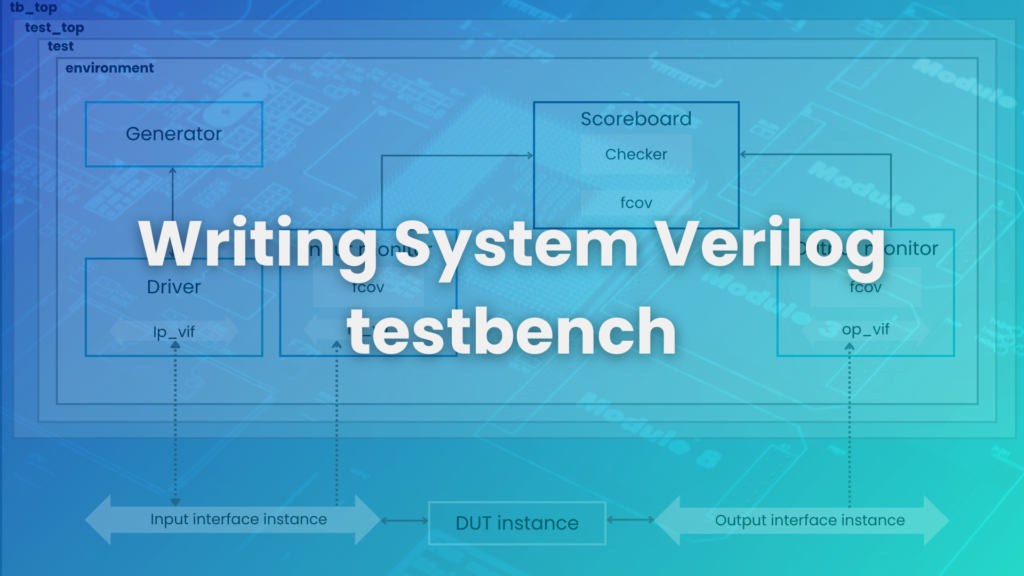

Online course that explains all the components in a System Verilog testbench and how they work together in fully verifying a Design Under Test. For a given Design description, the course explains how to arrive at a test plan, test bench architecture, and write a complete System Verilog testbench from scratch.

What will you learn?

-

Verification approach and methodology in the industry

- System Verilog testbench components

- Planning testbench architecture and its components

- Writing System Verilog testbench from scratch

Price Rs.7400 (inclusive of GST)

Instructor Viswa Krishnamuthi

Duration 4 Weeks

Chapters 5

Learners 136 students

This Course Includes

- 3 hours on-demand video

- Lab assignments

- Quizzes and Elaborate Questions

- Certificate of completion

Certificate for completion (80%):

The certificate will state:

“This is to certify that (Name) has actively participated

in the course ‘Digital Design and Verification’ and completed a major portion of the curriculum”

Certificate for completion (95% or more):

The certificate will state:

“This is to verify that(Name) has successfully

completed the course ‘Digital Design and Verification'”

Course Curriculum

5 Chapters 29 Lectures 3h total length

Video Preview with Icon Introduction _________________________________________________________________________________________________________________ 1 lecture 5min

Introduction _________________________________________________________________________________________________________________ 1 lecture 5min

- Introduction - --------------------------------------------------------------------------------------------------------05:11

Video Preview with Icon Test bench overview ______________________________________________________________________________________________________ _ 6 lectures 25min

Test bench overview ______________________________________________________________________________________________________ _ 6 lectures 25min

- Testbench introduction------------------------------------------------------------------------------------------------01.05

- Verification methodology----------------------------------------------------------------------------------------------07:38

- Testbench evolution------------------------------------------------------------ --------------------------------------02:28

- Procedural known answer testbench------------------------------------------------------------------------------------03:15

- File based testbench-------------------------------------------------------------------------------------------------- 01:54

- Constrained random functional coverage driven testbench--------------------------------------------------------------- 08:46

Video Preview with Icon Testbench components_____________________________________________________________________________________________________ 12 lectures 77min

Testbench components_____________________________________________________________________________________________________ 12 lectures 77min

- Chapter overview-------- ----------------------------------------------------------------------------------------------01:16

- Tb_top----------------------------------------------------------------------------------------------------------------04:12

- Test_top --------------------------------------------------------------------------------------------------------------03:25

- Config - ---------------------------------------------------------------------------------------------------------- ----03:12

- Test - -----------------------------------------------------------------------------------------------------------------02:55

- Environment - -------------------------------------------------------------------------------------------------------- -02:20

- Transaction - ----------------------------------------------------------------------------------------------------------02:40

- Generator - ----------------------------------------------------------------------------------------------- ------------02:09

- Driver - ----------------------------------------------------------------------------------------------------- ----------17:15

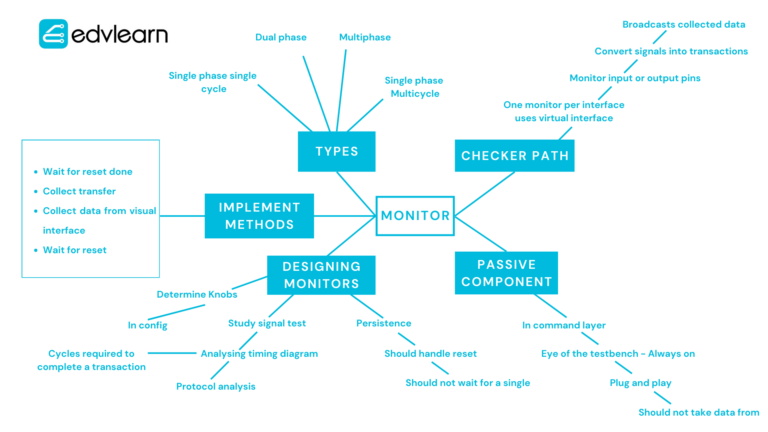

- Monitor - --------------------------------------------------------------------------------------------------------------13:56

- Scoreboard - ------------------------------------------------------------------------------------ ----------------------12:44

- Functional coverage - ------------------------------------------------------------------------------------------ --------04:45

- Chapter summary - -------------------------------------------------------------------------------------------- --------07:02

Video Preview with Icon Verification planning and testbench coding _______________________________________________________________________________ 7 lectures 63min

Verification planning and testbench coding _______________________________________________________________________________ 7 lectures 63min

- Verification planning---------------------------------------------------------------------------------------------------07:48

- Example 1: Router 1 DUT Description-------------------------------------------------------------------------------------- 03:21

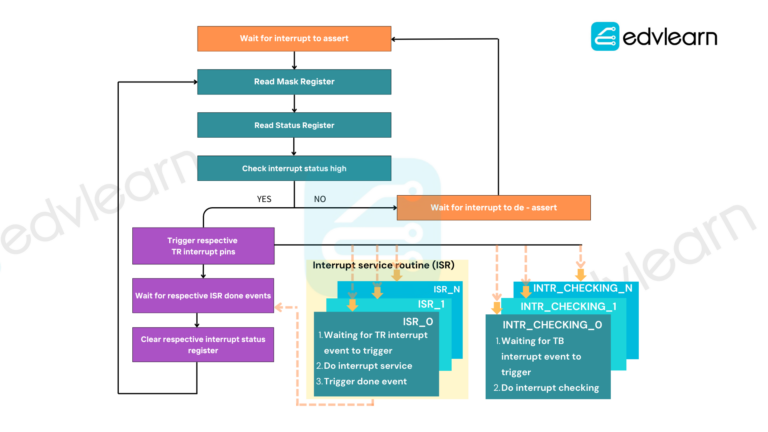

- Example 1: Router 1 Verification------------------------------------------------------------------------------------------ 18:06

- Example 2: Router 2 DUT Description ------------------------------------------------------------------------------------- 08:37

- Example 2: Router 2 Verification ----------------------------------------------------------------------------------------- 15:09

- Memory -------------------------------------------------------------------------------------------------------------- 03:31

- Memory verification ----------------------------------------------------------------------------------------------------06:32

Video Preview with Icon Coding assignments_________________________________________________________________________________________________________ 3 lectures 13min

Coding assignments_________________________________________________________________________________________________________ 3 lectures 13min

- Lab 1: Router 3 DUT description-------------------------------------------------------------------------------------------03:44

- Lab 2: Router 4 DUT description------------------------------------------------------------------------------------------ 05:16

- Lab 3: UART_Rx DUT description ------------------------------------------------------------------------------------------04:22

Meet Your Instructor

System Verilog language proficiency

Pre-requisite

Viswa Krishnamurthi

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience.

How it works?

Register

Sign up to gain access to the course

How it works?

How it works?

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Learn and Apply

Complete the course videos, exercises, and the exam

Get Certified

Share your certificates on LinkedIn and enhance your professional growth

To become a VLSI engineer, you need a good foundation in digital electronics. Proficiency in hardware description languages (HDL) like Verilog or VHDL and programming skills are essential for designing and verifying circuits. Strong problem-solving and analytical thinking skills help in optimizing designs.

Additionally, knowledge of simulation tools and debugging techniques can be beneficial. You should be comfortable to code

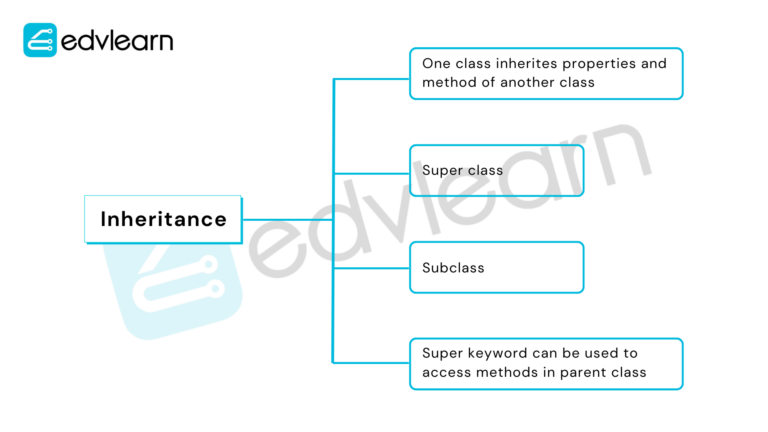

Yes! Our courses are designed to be beginner-friendly, with a structured curriculum that starts with the fundamentals before moving to advanced topics. Additionally, our trainers are available to assist you throughout your learning journey. Knowledge in programming helps in understanding the course.

Writing System Verilog Testbench

- Last Updated 01/2025

- English

- English[Integrated]

Online course that explains all the components in a System Verilog testbench and how they work together in fully verifying a Design Under Test. For a given Design description, the course explains how to arrive at a test plan, test bench architecture, and write a complete System Verilog testbench from scratch

What will you learn?

- Verification approach and methodology in the industry

- System Verilog test bench components

- Planning Testbench architecture and its components

- Writing System Verilog Test bench from scratch

Price Rs.7400 (inclusive of GST)

Instructor Viswa Krishnamurthi

Duration 4 Weeks

Chapters 14

Learners 193 students

This Course Includes:

- 3 hours on-demand video

- Lab assignments

- Quizzes and Elaborate Questions

- Certificate of completion

Certificate for completion (80%):

The certificate will state:

“This is to certify that (Name) has actively participated in the course ‘Digital Design and Verification’ and completed a major portion of the curriculum”

Certificate for completion (95% or more):

The certificate will state:

“This is to verify that(Name) has successfully completed the course ‘Digital Design and Verification'”

Course Curriculum

5 Chapters 29 Lectures 3h total length

Video Preview with Icon Introduction ____________________________________________________________ 1 lecture 5min

Introduction ____________________________________________________________ 1 lecture 5min

- Introduction-------------------------------------------------------------05:11

Video Preview with Icon Test bench overview _________________________________________________ _ 6 lectures 25min

Test bench overview _________________________________________________ _ 6 lectures 25min

- Testbench introduction--------------------------------------------------01.05

- Verification methodology------------------------------------------------07:38

- Testbench evolution---------------------------------------------------- 02:28

- Procedural known answer testbench--------------------------------------03:15

- File based testbench----------------------------------------------------01:54

- Constrained random functional coverage driven testbench----------------- 08:46

Video Preview with Icon Testbench components________________________________________________ 12 lectures 77min

Testbench components________________________________________________ 12 lectures 77min

- Chapter overview--------------------------------------------------------01:16

- Tb_top----------------------------------------------------------------- 04:12

- Test_top----------------------------------------------------------------03:25

- Config------------------------------------------------------------------03:12

- Test-------------------------------------------------------------------- 02:55

- Environment------------------------------------------------------------ 02:20

- Transaction-------------------------------------------------------------02:40

- Generator---------------------------------------------------------------02:09

- Driver--------------------------------------------------------- ----------17:15

- Monitor------------------------------------------------------------------13:56

- Scoreboard--------------------------------------------------------------12:44

- Functional coverage------------------------------------------------------04:45

- Chapter summary--------------------------------------------------------07:02

Video Preview with Icon Verification planning and testbench coding __________________________ 7 lectures 63min

Verification planning and testbench coding __________________________ 7 lectures 63min

- Verification planning---------------------------------------------------- 07:48

- Example 1: Router 1 DUT Description---------------------------------------- 03:21

- Example 1: Router 1 Verification-------------------------------------------- 18:06

- Example 2: Router 2 DUT Description----------------------------------------08:37

- Example 2: Router 2 Verification--------- ---------------------------------- 15:09

- Memory-----------------------------------------------------------------03:31

- Memory verification------------------------------------------------------ 06:32

Video Preview with Icon Coding assignments____________________________________________ ________ 3 lectures 13min

Coding assignments____________________________________________ ________ 3 lectures 13min

- Lab 1: Router 3 DUT description--------------------------------------------03:44

- Lab 2: Router 4 DUT description------------------------------------------- 05:16

- Lab 3: UART_Rx DUT description-------------------------------------------04:22

Meet Your Instructor

Pre-requisite

System Verilog language proficiency

Viswa Krishnamurthi

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience.

How it works?

How it works?

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Register

Sign up to gain access to the course

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Learn and Apply

Complete the course videos, exercises, and the exam.

Get Certified

Share your certificates on LinkedIn and enhance your professional growth

To become a VLSI engineer, you need a good foundation in digital electronics. Proficiency in hardware description languages (HDL) like Verilog or VHDL and programming skills are essential for designing and verifying circuits. Strong problem-solving and analytical thinking skills help in optimizing designs.

Additionally, knowledge of simulation tools and debugging techniques can be beneficial. You should be comfortable to code

Yes! Our courses are designed to be beginner-friendly, with a structured curriculum that starts with the fundamentals before moving to advanced topics. Additionally, our trainers are available to assist you throughout your learning journey. Knowledge in programming helps in understanding the course.

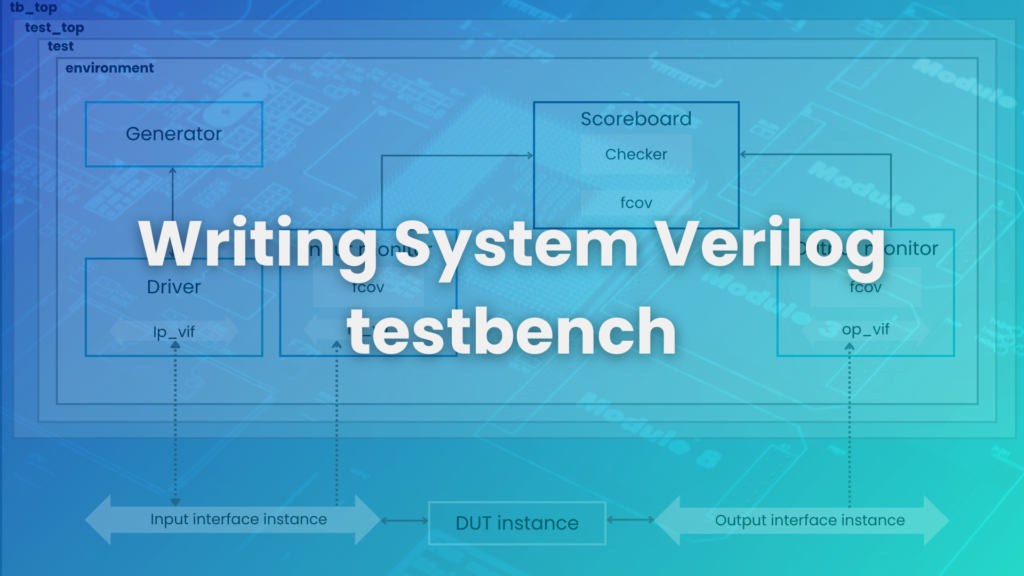

Writing System Verilog Testbench

Online course that explains all the components in a System Verilog testbench and how they work together in fully verifying a Design Under Test. For a given Design description, the course explains how to arrive at a test plan, test bench architecture, and write a complete System Verilog testbench from scratch

- Last Updated 01/2025

- English

- English[Integrated]

What will you learn?

- Verification approach and methodology in the industry

- System Verilog testbench components

- Planning testbench architecture and its components

- Writing System Verilog testbench from scratch

Price Rs.7400 (incl. of GST)

Instructor Viswa Krishnamurthi

Duration 4 Weeks

Chapters 5

Learners 193 students

This Course Includes

- 3 hours on-demand video

- Lab assignments

- Quizzes and Elaborate Questions

- Certificate of completion

Certificate for completion (80%):

The certificate will state:

“This is to certify that (Name) has actively participated in the course ‘Digital Design and Verification’ and completed a major portion of the curriculum”

Certificate for completion (95% or more):

The certificate will state:

“This is to verify that(Name) has successfully completed the course ‘Digital Design and Verification'”

Course Curriculum

5 Chapters 29 Lectures 3h total length

Video Preview with Icon Introduction _________________________________________________________________________________________________________________ 1 lecture 5min

Introduction _________________________________________________________________________________________________________________ 1 lecture 5min

- Introduction-------- 05:11

Video Preview with Icon Test bench overview ________________________________ 6 lectures 25min

Test bench overview ________________________________ 6 lectures 25min

- Testbench introduction--01.05

- Verification methodology---------------------------07:38

- Testbench evolution-- -02:28

- Procedural known answer testbench-------------03:15

- File based testbench--- 01:54

- Constrained random functional coverage driven testbench------------ 08:46

Video Preview with Icon Testbench components__________________ 12 lectures 77min

Testbench components__________________ 12 lectures 77min

- Chapter overview-----01:16

- Tb_top-- ------------04:12

- Test_top-------------03:25

- Config---------------03:12

- Test-----------------02:55

- Environment--------- 02:20

- Transaction----------02:40

- Generator----------- 02:09

- Driver--------------- 17:15

- Monitor--------------13:56

- Scoreboard----------12:44

- Functional coverage - 04:45

- Chapter summary----07:02

Video Preview with Icon Verification planning and

testbench coding _______________________________________________________________________________ 7 lectures 63min

Verification planning and

testbench coding _______________________________________________________________________________ 7 lectures 63min

- Verification planning--07:48

- Example 1: Router 1 DUT Description-----------03:21

- Example 1: Router 1 Verification-----------18:06

- Example 2: Router 2 DUT Description-----------08:37

- Example 2: Router 2 Verification-----------15:09

- Memory--------------03:31

- Memory verification ---06:32

Video Preview with Icon Coding assignments_________________________________________________________________________________________________________ 3 lectures 13min

Coding assignments_________________________________________________________________________________________________________ 3 lectures 13min

- Lab 1: Router 3 DUT description---------------------03:44

- Lab 2: Router 4 DUT description----------05:16

- Lab 3: UART_Rx DUT description----------04:22

How it works?

Meet Your Instructor

Viswa Krishnamurthi

Viswa is the Founder and CEO of Edveon, a semiconductor product and services company. Viswa has 10 years of Design Verification experience and 15 years of RTL Design experience.

System Verilog language proficiency

Pre-requisite

Register

Sign up to gain access to the course

Faculty Allocation

After enrolling in the course, a dedicated faculty will be assigned to guide and support

Learn and Apply

Complete the course videos, exercises, and the exam.

Get Certified

Share your certificates on LinkedIn and enhance your professional growth

To become a VLSI engineer, you need a good foundation in digital electronics. Proficiency in hardware description languages (HDL) like Verilog or VHDL and programming skills are essential for designing and verifying circuits. Strong problem-solving and analytical thinking skills help in optimizing designs.

Additionally, knowledge of simulation tools and debugging techniques can be beneficial. You should be comfortable to code

Yes! Our courses are designed to be beginner-friendly, with a structured curriculum that starts with the fundamentals before moving to advanced topics. Additionally, our trainers are available to assist you throughout your learning journey. Knowledge in programming helps in understanding the course.